处理器内存模型

内存模型划分

放松程序中写-读操作的顺序,由此产生了Total Store Ordering内存模型(简称为TSO)。

在上面的基础上,继续放松程序中写-写操作的顺序,由此产生了Partial Store Order内存模型(简称为PSO)。

在前面两条的基础上,继续放松程序中读-写和读-读操作的顺序,由此产生了RelaxedMemory Order内存模型(简称为RMO)和PowerPC内存模型。

这里处理器对读/写操作的放松,是以两个操作之间不存在数据依赖性为前提的。

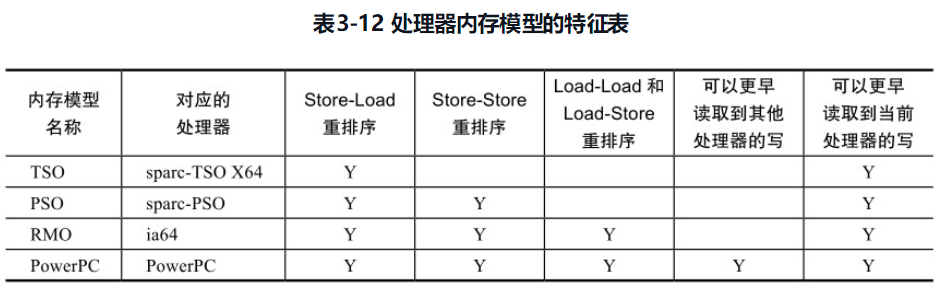

从表3-12中可以看到,所有处理器内存模型都允许写-读重排序,原因在第1章已经说明过:它们都使用了写缓存区。写缓存区可能导致写-读操作重排序。同时,我们可以看到这些处理器内存模型都允许更早读到当前处理器的写,原因同样是因为写缓存区。由于写缓存区仅对当前处理器可见,这个特性导致当前处理器可以比其他处理器先看到临时保存在自己写缓存区中的写。表3-12中的各种处理器内存模型,从上到下,模型由强变弱。越是追求性能的处理器,内存模型设计得会越弱。因为这些处理器希望内存模型对它们的束缚越少越好,这样它们就可以做尽可能多的优化来提高性能。

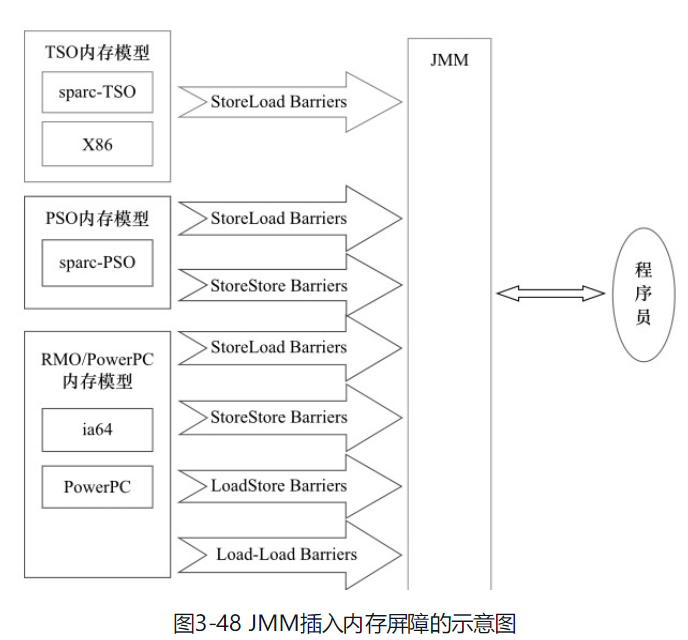

由于常见的处理器内存模型比JMM要弱,Java编译器在生成字节码时,会在执行指令序列的适当�位置插入内存屏障来限制处理器的重排序。同时,由于各种处理器内存模型的强弱不同,为了在不同的处理器平台向程序员展示一个一致的内存模型,JMM在不同的处理器中需要插入的内存屏障的数量和种类也不相同。

JMM屏蔽了不同处理器内存模型的差异,它在不同的处理器平台之上为Java程序员呈现了一个一致的内存模型。

各种内存模型之间的关系

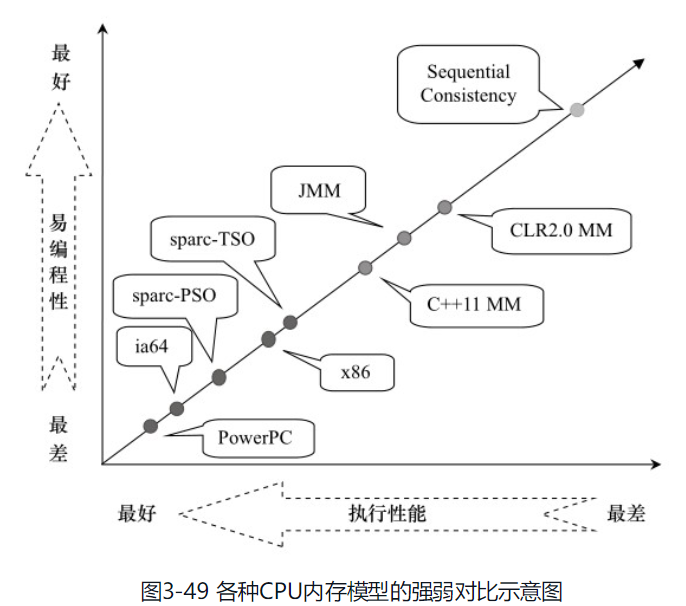

JMM是一个语言级的内存模型,处理器内存模型是硬件级的内存模型,顺序一致性内存模型是一个理论参考模型。下面是语言内存模型、处理器内存模型和顺序一致性内存模型的强弱对比示意图,如图3-49所示。

从图中可以看出:常见的4种处理器内存模型比常用的3种语言内存模型要弱,处理器内存模型和语言内存模型都比顺序一致性内存模型要弱。同处理器内存模型一样,越是追求执行性能的语言,内存模型设计得会越弱。

JMM的内存可见性保证

-

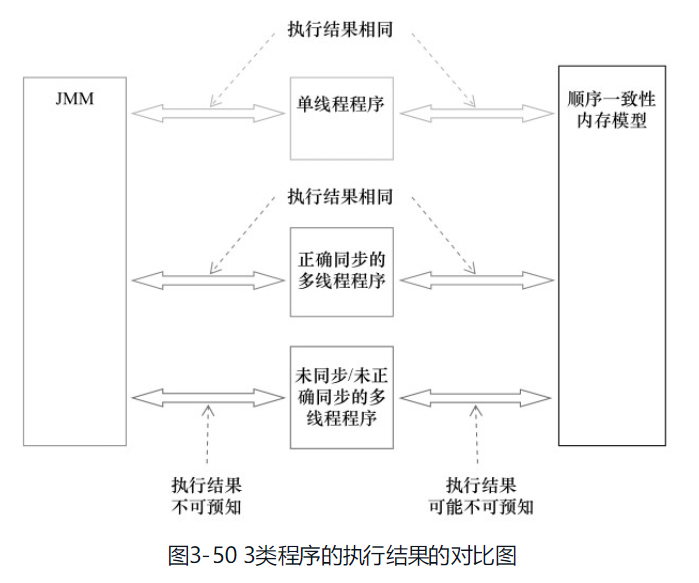

单线程程序。单线程程序不会出现内存可见性问题。编译器、runtime和处理器会共同确保单线程程序的执行结果与该程序在顺序一致性模型中的执行结果相同。

-

正确同步的多线程程序。正确同步的多线程程序的执行将具有顺序一致性(程序的执行结果与该程序在顺序一致性内存模型中的执行结果相同)。这是JMM关注的重点,JMM通过限制编译器和处理器的重排序来为程序员提供内存可见性保证。

-

未同步/未正确同步的多线程程序。JMM为它们提供了最小安全性保障:线程执行时读取到的值,要么是之前某个线程写入的值,要么是默认值(0、null、false)。

最小安全性保障与64位数据的非原子性写并不矛盾。它们是两个不同的概念,它们“发生”的时间点也不同。

最小安全性“发生”在对象被任意线程使用之前。64位数据的非原子性写“发生”在对象被多个线程使用的过程中(写共享变量)。

64位数据的非原子性写“发生”在对象被多个线程使用的过程中(写共享变量)。当发生问题时(处理器B看到仅仅被处理器A“写了一半”的无效值),这里虽然处理器B读取到一个被写了一半的无效值,但这个值仍然是处理器A写入的,只不过是处理器A还没有写完而已。

最小安全性保证线程读取到的值,要么是之前某个线程写入的值,要么是默认值(0、null、false)。但最小安全性并不保证线程读取到的值,一定是某个线程写完后的值。最小安全性保证线程读取到的值不会无中生有的冒出来,但并不保证线程读取到的值一定是正确的。

JSR-133对旧内存模型的修补

增强volatile的内存语义。旧内存模型允许volatile变量与普通变量重排序。JSR-133严格限制volatile变量与普通变量的重排序,使volatile的写-读和锁的释放-获取具有相同的内存语义。

增强final的内存语义。在旧内存模型中,多次读取同一个final变量的值可能会不相同。为此,JSR-133为final增加了两个重排序规则。在保证final引用不会从构造函数内逸出的情况下,final具有了初始化安全性。

java线程状态

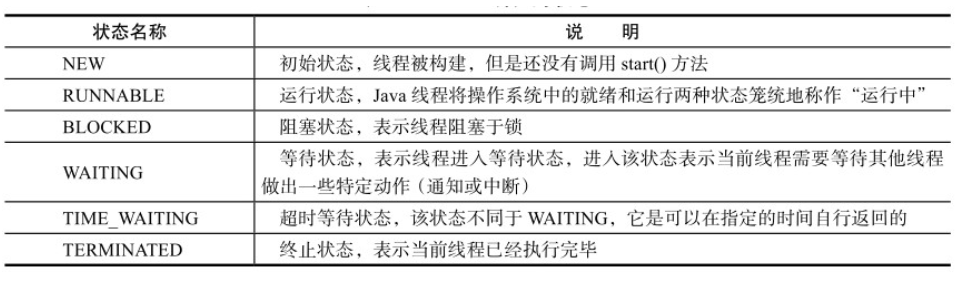

线程状态

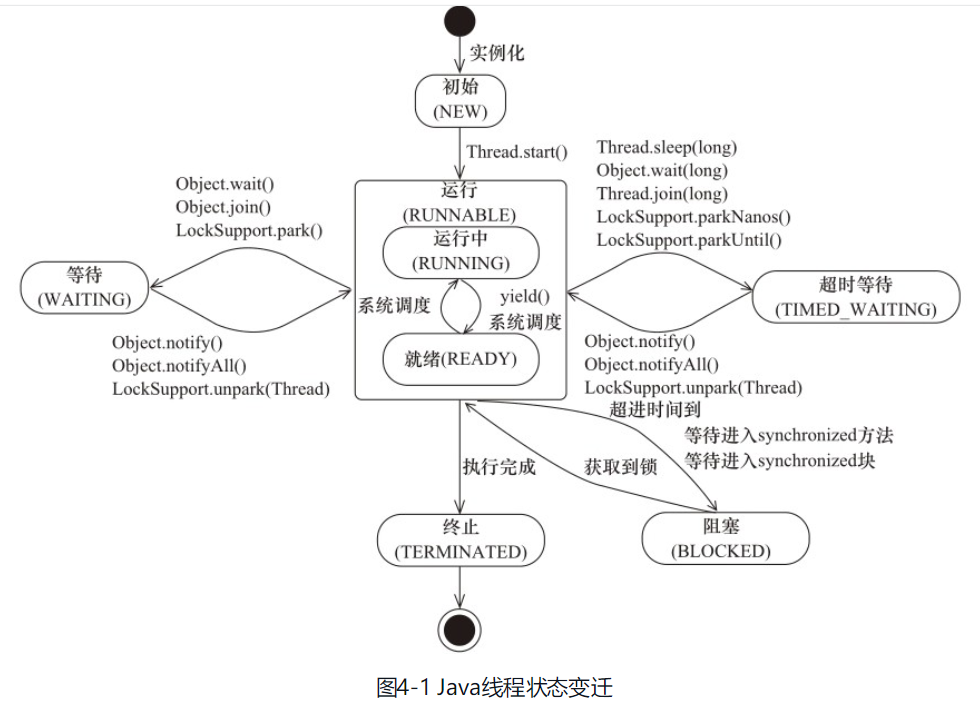

线程状态之间的变化

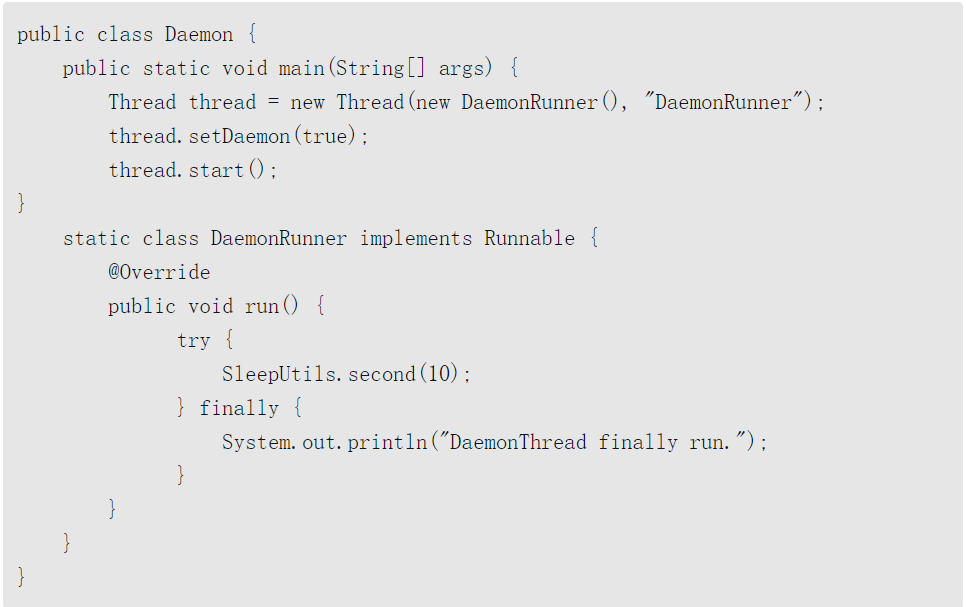

Daemon线程

Daemon线程被用作完成支持性工作,但是在Java虚拟机退出时Daemon线程中的finally块并不一定会执行。

main线程(非Daemon线程)在启动了线程DaemonRunner之后随着main方法执行完毕而终止,而此时Java虚拟机中已经没有非Daemon线程,虚拟机需要退出。Java虚拟机中的所有Daemon线程都需要立即终止,因此DaemonRunner立即终止,但是DaemonRunner中的finally块并没有执行。

main线程(非Daemon线程)在启动了线程DaemonRunner之后随着main方法执行完毕而终止,而此时Java虚拟机中已经没有非Daemon线程,虚拟机需要退出。Java虚拟机中的所有Daemon线程都需要立即终止,因此DaemonRunner立即终止,但是DaemonRunner中的finally块并没有执行。

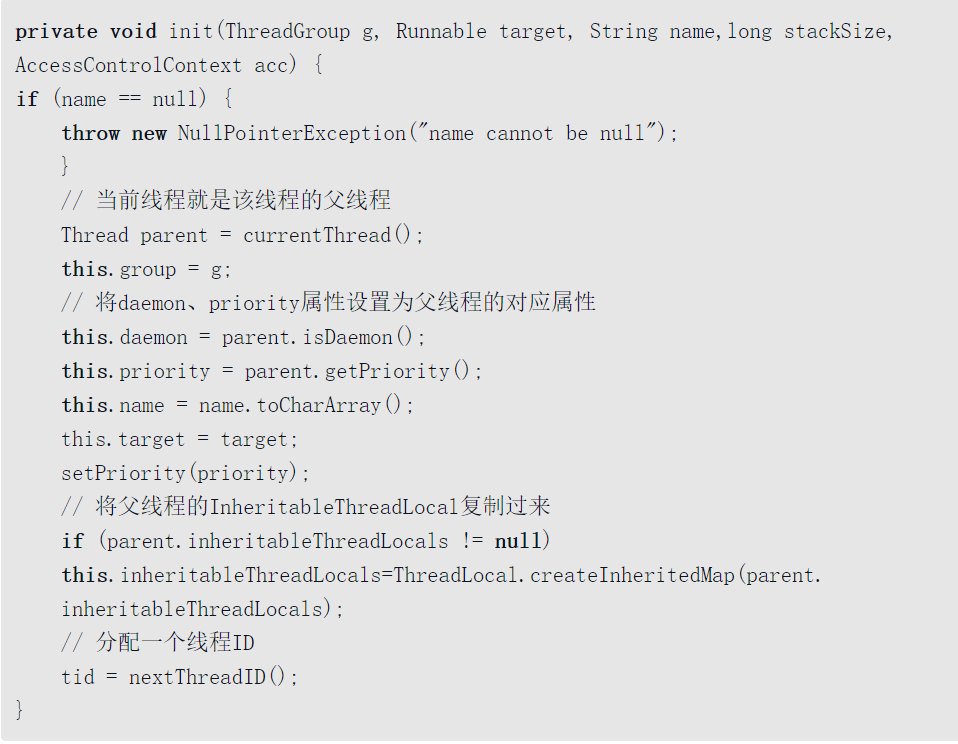

线�程如何初始化

一个新构造的线程对象是由其parent线程来进行空间分配的,而child线程继承了parent是否为Daemon、优先级和加载资源的contextClassLoader以及可继承的ThreadLocal,同时还会分配一个唯一的ID来标识这个child线程。至此,一个能够运行的线程对象就初始化好了,在堆内存中等待着运行。

线程start()方法的含义是:当前线程(即parent线程)同步告知Java虚拟机,只要线程规划器空闲,应立即启动调用start()方法的线程。

线程中断 和 中断异常

中断好比其他线程对该线程打了个招呼,其他线程通过调用该线程的interrupt()方法对其进行中断操作。

线程通过检查自身是否被中断来进行响应,线程通过方法isInterrupted()来进行判断是否被中断,也可以调用静态方法Thread.interrupted()对当前线程的中断标识位进行复位。如果该线程已经处于终结状态,即使该线程被中断过,在调用该线程对象的isInterrupted()时依旧会返回false。

从Java的API中可以看到,许多声明抛出InterruptedException的方法(例如Thread.sleep(long millis)方法)这些方法在抛出InterruptedException之前,Java虚拟机会先将该线程的中断标识位清除,然后抛出InterruptedException,此时调用isInterrupted()方法将会返回false。

Interrupted

public class Interrupted {

public static void main(String[] args) throws Exception {

// sleepThread不停的尝试睡眠

Thread sleepThread = new Thread(new SleepRunner(), "SleepThread");

sleepThread.setDaemon(true);

// busyThread不停的运行

Thread busyThread = new Thread(new BusyRunner(), "BusyThread");

busyThread.setDaemon(true);

sleepThread.start();

busyThread.start();

// 休眠5秒,让sleepThread和busyThread充分运行

TimeUnit.SECONDS.sleep(5);

sleepThread.interrupt();

busyThread.interrupt();

System.out.println("SleepThread interrupted is " + sleepThread.isInterrupted());

System.out.println("BusyThread interrupted is " + busyThread.isInterrupted());

// 防止sleepThread和busyThread立刻退出

SleepUtils.second(2);

}

static class SleepRunner implements Runnable {

@Override

public void run() {

while (true) {

SleepUtils.second(10);

}

}

}

static class BusyRunner implements Runnable {

@Override

public void run() {

while (true) {

}

}

}

}

抛出InterruptedException的线程SleepThread,其中断标识位被清除了,而一直忙碌运作的线程BusyThread,中断标识位没有被清除。

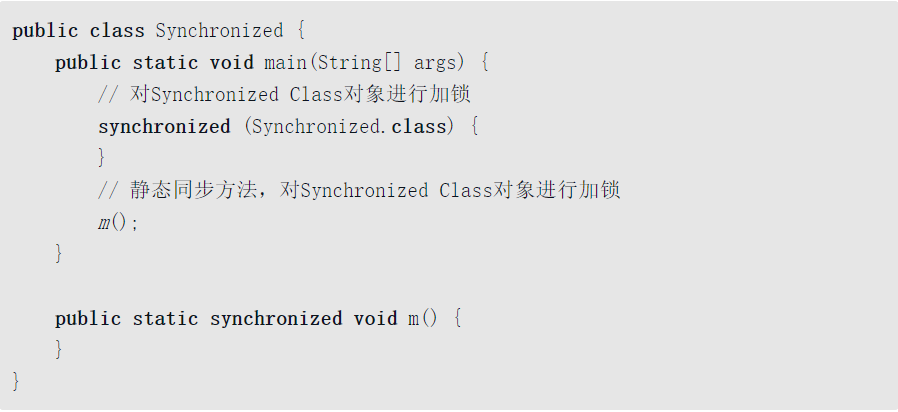

synchronized实现细节

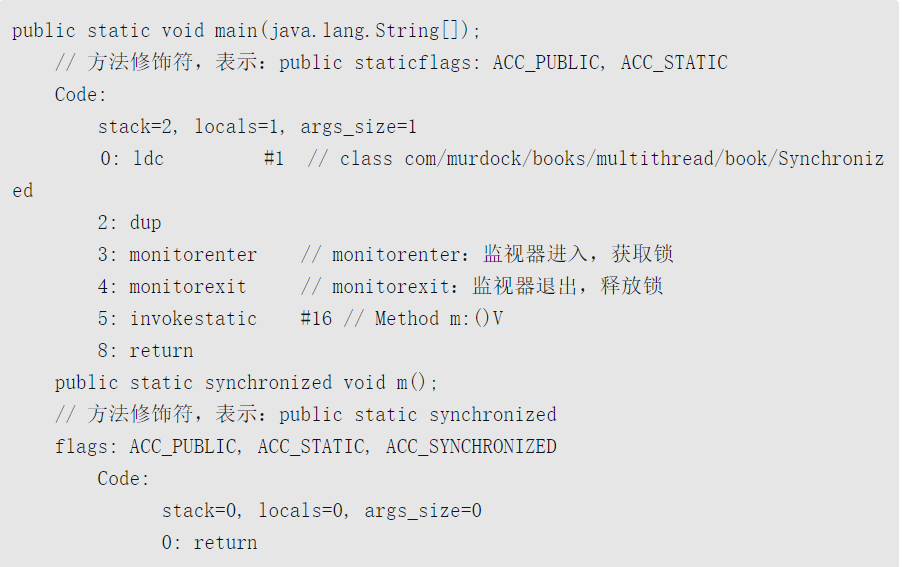

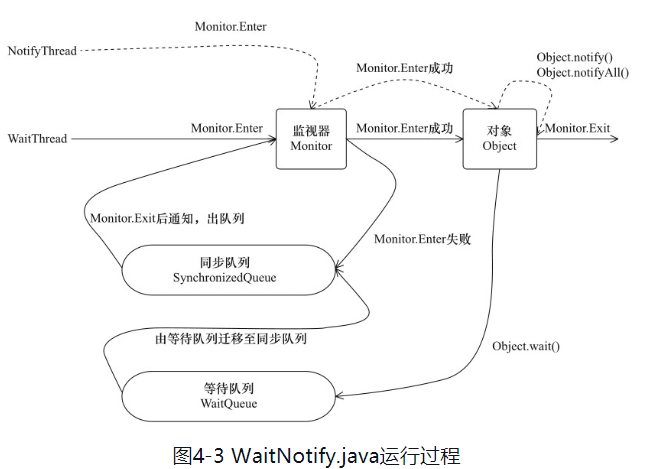

本质是对一个对象的监视器(monitor)进行获取,而这个获取过程是排他的,也就是同一时刻只能有一个线程获取到由synchronized所保护对象的监视器。

一个线程对Object(Object由synchronized保护)的访问,首先要获得Object的监视器。如果获取失败,线程进入同步队列,线程状态变为BLOCKED。当访问Object 的前驱(获得了锁的线程)释放了锁,则该释放操作唤醒阻塞在同步队列中的线程,使其重新尝试对监视器的获取。

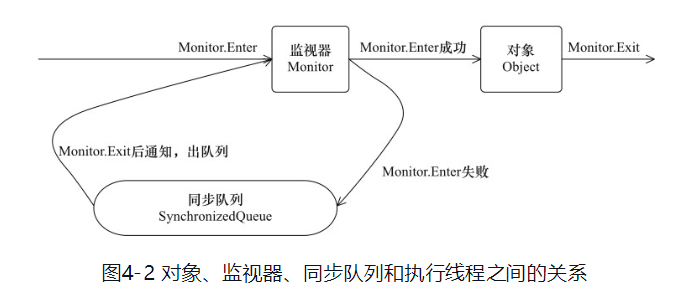

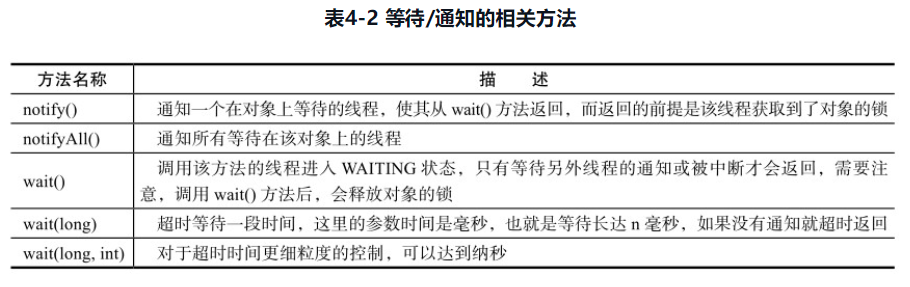

等待通知

等待/通知机制,是指一个线程A调用了对象O的wait()方法进入等待状态,而另一个线程B调用了对象O的notify()或者notifyAll()方法,线程A收到通知后从对象O的wait()方法返回,进而执行后续操作。上述两个线程通过对象O来完成交互,而对象上的wait()和notify/notifyAll()的关系就如同开关信号一样,用来完成等待方和通知方之间的交互工作。

WaitNotify

public class WaitNotify {

static boolean flag = true;

static Object lock = new Object();

public static void main(String[] args) throws Exception {

Thread waitThread = new Thread(new Wait(), "WaitThread");

waitThread.start();

TimeUnit.SECONDS.sleep(1);

Thread notifyThread = new Thread(new Notify(), "NotifyThread");

notifyThread.start();

}

static class Wait implements Runnable {

public void run() {

// 加锁,拥有lock的Monitor

synchronized (lock) {

// 当条件不满足时,继续wait,同时释放了lock的锁

while (flag) {

try {

System.out.println(Thread.currentThread()+ " flagistrue.wait

@ " + new SimpleDateFormat("HH:mm:ss").format(new Date()));

lock.wait();

} catch (InterruptedException e) {

}

}

// 条件满足时,完成工作

System.out.println(Thread.currentThread() + " flag is false. running

@ " + new SimpleDateFormat("HH:mm:ss").format(new Date()));

}

}

}

static class Notify implements Runnable {

public void run() {

// 加锁,拥有lock的Monitor

synchronized (lock) {

// 获取lock的锁,然后进行通知,通知时不会释放lock的锁,

// 直到当前线程释放了lock后,WaitThread才能从wait方法中返回

System.out.println(Thread.currentThread() + " hold lock. notify @ " +

new SimpleDateFormat("HH:mm:ss").format(new Date()));

lock.notifyAll();

flag = false;

SleepUtils.second(5);

}

// 再次加锁

synchronized (lock) {

System.out.println(Thread.currentThread() + " hold lock again. sleep

@ " + new SimpleDateFormat("HH:mm:ss").format(new Date()));

SleepUtils.second(5);

}

}

}

}

SleepUtils

public class SleepUtils {

public static final void second(long seconds) {

try {

TimeUnit.SECONDS.sleep(seconds);

} catch (InterruptedException e){

}

}

}

调用wait()、notify()以及notifyAll()时需要注意的细节

- 使用wait()、notify()和notifyAll()时需要先对调用对象加锁。

- 调用wait()方法后,线程状态由RUNNING变为WAITING,并将当前线程放置到对象的等待队列。

- notify()或notifyAll()方法调用后,等待线程依旧不会从wait()返回,需要调用notify()或notifAll()的线程释放锁之后,等待线程才有机会从wait()返回。

- notify()方法将等待队��列中的一个等待线程从等待队列中移到同步队列中,而notifyAll()方法则是将等待队列中所有的线程全部移到同步队列,被移动的线程状态由WAITING变为BLOCKED。

- 从wait()方法返回的前提是获得了调用对象的锁。

WaitThread首先获取了对象的锁,然后调用对象的wait()方法,从而放弃了锁并进入了对象的等待队列WaitQueue中,进入等待状态。由于WaitThread释放了对象的锁,NotifyThread随后获取了对象的锁,并调用对象的notify()方法,将WaitThread从WaitQueue移到SynchronizedQueue中,此时WaitThread的状态变为阻塞状态。NotifyThread释放了锁之后,WaitThread再次获取到锁并从wait()方法返回继续执行。

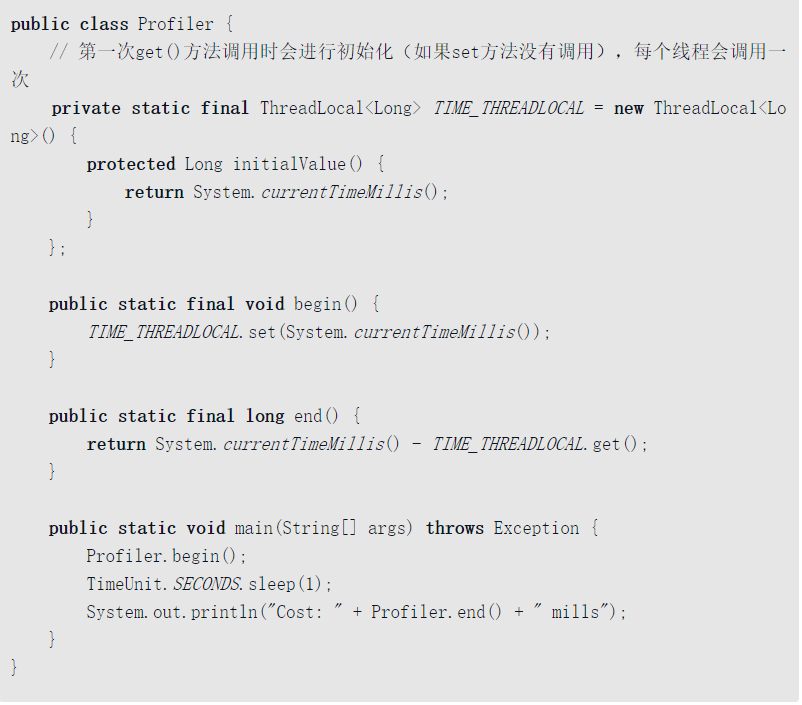

ThreadLocal 变量使用

连接池案例 连接数增加则总链接数增加,同时为获取到的比例也在增加

ConnectionPool

/**

* 从连接池中获取、使用和释放连接的过程,

* 而客户端获取连接的过程被设定为等待超时的模式,

* 也就是在1000毫秒内如果无法获取到可用连接,

* 将会返回给客户端一个null。设定连接池的大小为10个,

* 然后通过调节客户端的线程数来模拟无法获取连接的场景。

*/

public class ConnectionPool {

private LinkedList<Connection> pool = new LinkedList<Connection>();

public ConnectionPool(int initialSize) {

if (initialSize > 0) {

for (int i = 0; i < initialSize; i++) {

pool.addLast(ConnectionDriver.createConnection());

}

}

}

public void releaseConnection(Connection connection) {

if (connection != null) {

synchronized (pool) {

// 连接释放后需要进行通知,这样其他消费者能够感知到连接池中已经归还了一个连接

pool.addLast(connection);

pool.notifyAll();

}

}

}

// 在mills内无法获取到连接,将会返回null

public Connection fetchConnection(long mills) throws InterruptedException {

synchronized (pool) {

// 完全�超时

if (mills <= 0) {

while (pool.isEmpty()) {

pool.wait();

}

return pool.removeFirst();

} else {

long future = System.currentTimeMillis() + mills;

long remaining = mills;

while (pool.isEmpty() && remaining > 0) {

pool.wait(remaining);

remaining = future - System.currentTimeMillis();

}

Connection result = null;

if (!pool.isEmpty()) {

result = pool.removeFirst();

}

return result;

}

}

}

}

ConnectionDriver

/**

* 我们通过动态代理构造了一个Connection,该Connection的代理实现仅仅

* 是在commit()方法调用时休眠100毫秒

*/

public class ConnectionDriver {

static class ConnectionHandler implements InvocationHandler {

@Override

public Object invoke(Object proxy, Method method, Object[] args) throws Throwable {

if (method.getName().equals("commit")) {

TimeUnit.MILLISECONDS.sleep(100);

}

return null;

}

}

// 创建一个Connection的代理,在commit时休眠100毫秒

public static final Connection createConnection() {

return (Connection) Proxy.newProxyInstance(ConnectionDriver.class.getClassLoader(),

new Class<?>[] { Connection.class }, new ConnectionHandler());

}

}

ConnectionPoolTest

/**

* 使用了CountDownLatch来确保ConnectionRunnerThread能够同时开始执行,

* 并且在全部结束之后,才使main线程从等待状态中返回。

* 当前设定的场景是10个线程同时运行获取连接池(10个连接)中的连接,

* 通过调节线程数量来观察未获取到连接的情况

*/

public class ConnectionPoolTest {

static ConnectionPool pool = new ConnectionPool(10);

// 保证所有ConnectionRunner能够同时开始

static CountDownLatch start = new CountDownLatch(1);

// main线程将会等待所有ConnectionRunner结束后才能继续执行

static CountDownLatch end;

public static void main(String[] args) throws Exception {

// 线程数量,可以修改线程数量进行观察

int threadCount = 10;

end = new CountDownLatch(threadCount);

int count = 20;

AtomicInteger got = new AtomicInteger();

AtomicInteger notGot = new AtomicInteger();

for (int i = 0; i < threadCount; i++) {

Thread thread = new Thread(new ConnetionRunner(count, got, notGot),

"ConnectionRunnerThread");

thread.start();

}

start.countDown();

end.await();

System.out.println("total invoke: " + (threadCount * count));

System.out.println("got connection: " + got);

System.out.println("not got connection " + notGot);

}

static class ConnetionRunner implements Runnable {

int count;

AtomicInteger got;

AtomicInteger notGot;

public ConnetionRunner(int count, AtomicInteger got, AtomicInteger notGot) {

this.count = count;

this.got = got;

this.notGot = notGot;

}

public void run() {

try {

start.await();

} catch (Exception ex) {

}

while (count > 0) {

try {

// 从线程池中获取连接,如果1000ms内无法获取到,将会返回null

// 分别统计连接获取的数量got和未获取到的数量notGot

Connection connection = pool.fetchConnection(1000);

if (connection != null) {

try {

connection.createStatement();

connection.commit();

} finally {

pool.releaseConnection(connection);

got.incrementAndGet();

}

} else {

notGot.incrementAndGet();

}

} catch (Exception ex) {

} finally {

count--;

}

}

end.countDown();

}

}

}

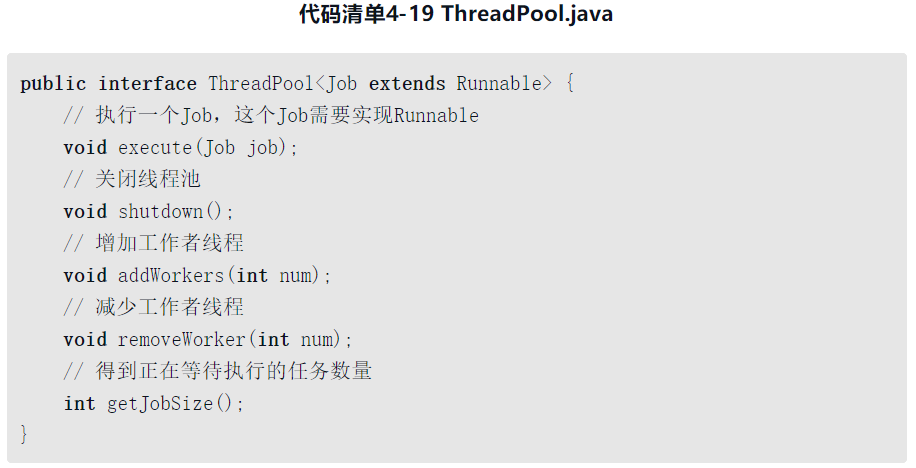

线程池

DefaultTheadPool

public class DefaultThreadPool<Job extends Runnable> implements ThreadPool<Job> {

// 线程池最大限制数

private static final intMAX_WORKER_NUMBERS = 10;

// 线程池默认的数量

private static final int DEFAULT_WORKER_NUMBERS = 5;

// 线程池最小的数量

private static final int MIN_WORKER_NUMBERS= 1;

// 这是一个工作列表,将会向里面插入工作

private final LinkedList<Job> jobs = new LinkedList<Job>();

// 工作者列表

private final List<Worker> workers = Collections.synchronizedList(new

ArrayList<Worker>());

// 工作者线程的数量

private int workerNum = DEFAULT_WORKER_NUMBERS;

// 线程编号生成

private AtomicLong threadNum = new AtomicLong();

public DefaultThreadPool() {

initializeWokers(DEFAULT_WORKER_NUMBERS);

}

public DefaultThreadPool(int num) {

workerNum = num > MAX_WORKER_NUMBERS ? MAX_WORKER_NUMBERS : num < MIN_WORKER_

NUMBERS ? MIN_WORKER_NUMBERS : num;

initializeWokers(workerNum);

}

public void execute(Job job) {

if (job != null) {

// �添加一个工作,然后进行通知

synchronized (jobs) {

jobs.addLast(job);

jobs.notify();

}

}

}

public void shutdown() {

for (Worker worker : workers) {

worker.shutdown();

}

}

public void addWorkers(int num) {

synchronized (jobs) {

// 限制新增的Worker数量不能超过最大值

if (num + this.workerNum > MAX_WORKER_NUMBERS) {

num = MAX_WORKER_NUMBERS - this.workerNum;

}

initializeWokers(num);

this.workerNum += num;

}

}

public void removeWorker(int num) {

synchronized (jobs) {

if (num >= this.workerNum) {

throw new IllegalArgumentException("beyond workNum");

}

// 按照给定的数量停止Worker

int count = 0;

while (count < num) {

Worker worker = workers.get(count)

if (workers.remove(worker)) {

worker.shutdown();

count++;

}

}

this.workerNum -= count;

}

}

public int getJobSize() {

return jobs.size();

}

// 初始化线程工作者

private void initializeWokers(int num) {

for (int i = 0; i < num; i++) {

Worker worker = new Worker();

workers.add(worker);

Thread thread = new Thread(worker, "ThreadPool-Worker-" + threadNum.

incrementAndGet());

thread.start();

}

}

// 工作者,负责消费任务

class Worker implements Runnable {

// 是否工作

private volatile boolean running= true;

public void run() {

while (running) {

Job job = null;

synchronized (jobs) {

// 如果工作者列表是空的,那么就wait

while (jobs.isEmpty()) {

try {

jobs.wait();

} catch (InterruptedException ex) {

// 感知到外部对WorkerThread的中断操作,返回

Thread.currentThread().interrupt();

return;

}

}

// 取出一个Job

job = jobs.removeFirst();

}

if (job != null) {

try {

job.run();

} catch (Exception ex) {

// 忽略Job执行中的Exception

}

}

}

}

public void shutdown() {

running = false;

}

}

}

参考资料

- 书籍名称:《java并发编程的艺术》 作者:方腾飞 魏鹏 程晓明

-

本作品代码部分采用 Apache 2.0协议进行许可。遵循许可的前提下,你可以自由地对代码进行修改,再发布,可以将代码用作商业用途。但要求你:

- 署名:在原有代码和衍生代码中,保留原作者署名及代码来源信息。

- 保留许可证:在原有代码和衍生代码中,保留Apache 2.0协议文件。

-

本作品文档部分采用知识共享署名 4.0 国际许可协议进行许可。 遵循许可的前提下,你可以自由地共享,包括在任何媒介上以任何形式复制、发行本作品,亦可以自由地演绎、修改、转换或以本作品为基础进行二次创作。但要求你:

- 署名:应在使用本文档的全部或部分内容时候,注明原作者及来源信息。

- 非商业性使用:不得用于商业出版或其他任何带有商业性质的行为。如需商业使用,请联系作者。

- 相同方式共享的条件:在本文档基础上演绎、修改的作品,应当继续以知识共享署名 4.0国际许可协议进行许可。